- 이전 글

(1) RTL : https://chonh0531.tistory.com/2

SPI 통신 - (1) RTL

목차1. 배경2. 과제 정의 및 개요3. 소스코드4. 시뮬레이션 결과 1. 배경모든 칩은 통신이 필요하기 때문에 통신 모듈이 들어가있습니다.그중에서 좀 기본적인 통신 모듈중 하나인 SPI통신을 이

chonh0531.tistory.com

목차

1. 합성 코드

2. Pre-Layout Simulation

3. P&R

4. Post-Layout Simulation

1. 합성 코드

리눅스 환경에서 진행하였으며, 디렉토리는 다음과 같습니다.

SPI ─ SIM ─ function_SIM ─ [SPI_Slave.v , tb_SPI_Slave.v]

└ pre_SIM ─ [tb_SPI_Slave_pre.v]

└ post_SIM ─ [tb_SPI_Slave_post.v]

└ SYN ─ RTL ─ [constraints.sdc , run_genus.tcl]

└ Report ─ [ ... ]

└ Output ─ [SPI_Slave_netlist.v , SPI_Slave_sdc.sdc , delays.sdf]

└ PNR ─ [ SPI_Slave_GDS.gds , SPI_Slave_PNR.v , SPI_Slave_delay_PNR.sdf]

└ timingReports ─ [SPI_Slave_preCTS_all.tarpt , SPI_Slave_postCTS_all.tarpt, SPI_Slave_postRoute_all.tarpt]

Tool은 Genus를 사용하였으며 라이브러리는 교육용 라이브러리 사용하였습니다.

스크립트 코드는 다음과 같습니다.

## run_genus.tcl

set_db init_lib_search_path ../../../LIB/lib/

set_db init_hdl_search_path ../../SIM/function_SIM/

read_libs slow_vdd1v0_basicCells.lib

read_hdl SPI_Slave.v

elaborate

read_sdc ./constraints.sdc

set_db syn_generic_effort medium

set_db syn_map_effort medium

set_db syn_opt_effort medium

syn_generic

syn_map

syn_opt

#reports

report_timing > ../Report/report_timing.rpt

report_power > ../Report/report_power.rpt

report_area > ../Report/report_area.rpt

report_qor > ../Report/report_qor.rpt

#Outputs

write_hdl > ../Output/SPI_Slave_netlist.v

write_sdc > ../Output/SPI_Slave_sdc.sdc

write_sdf -timescale ns -nonegchecks -recrem split -edges check_edge -setuphold split > ../Output/delays.sdf

Constraint는 지금 단계에서는 간단하게 clock 설정만 하겠습니다.

create_clock -name i_SCLK -period 40 -waveform {0 5} [get_ports "i_SCLK"]

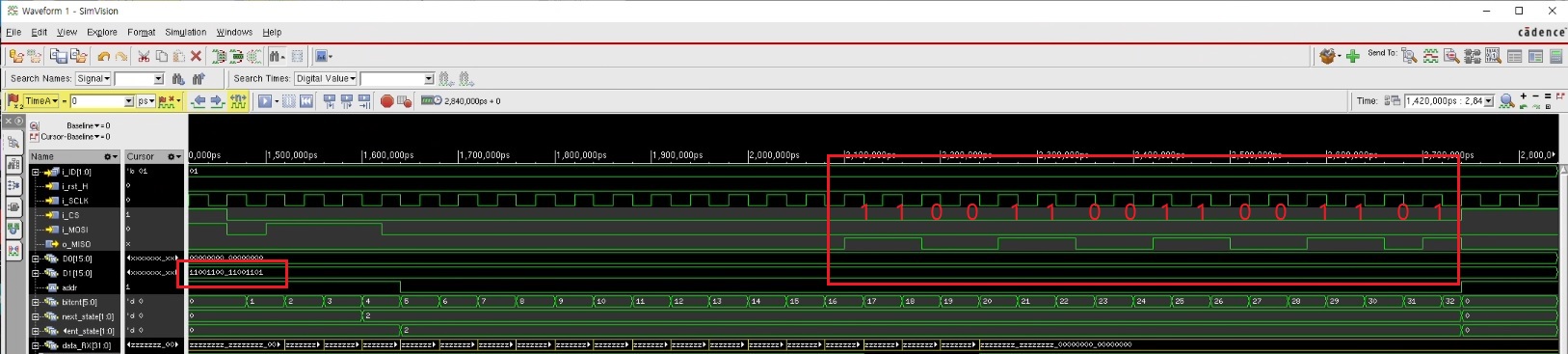

2. Pre-Layout Simulation

합성 결과로 나온 SPI_Slave_netlist.v 파일과,

delay 정보를 포함시킨 tb_SPI_Slave_pre.v 파일 및 라이브러리를 컴파일시켜

시뮬레이션을 진행하였습니다.

Tool은 역시 Xcelium을 사용하였습니다.

이전에 했던 Function Simulation과 동일하게 작동하는 것을 확인할 수 있습니다.

사진에는 복잡하여 보이지 않았으나, 각 gate들에 연결된 wire들이 있고, delay는 적용되어 있습니다.

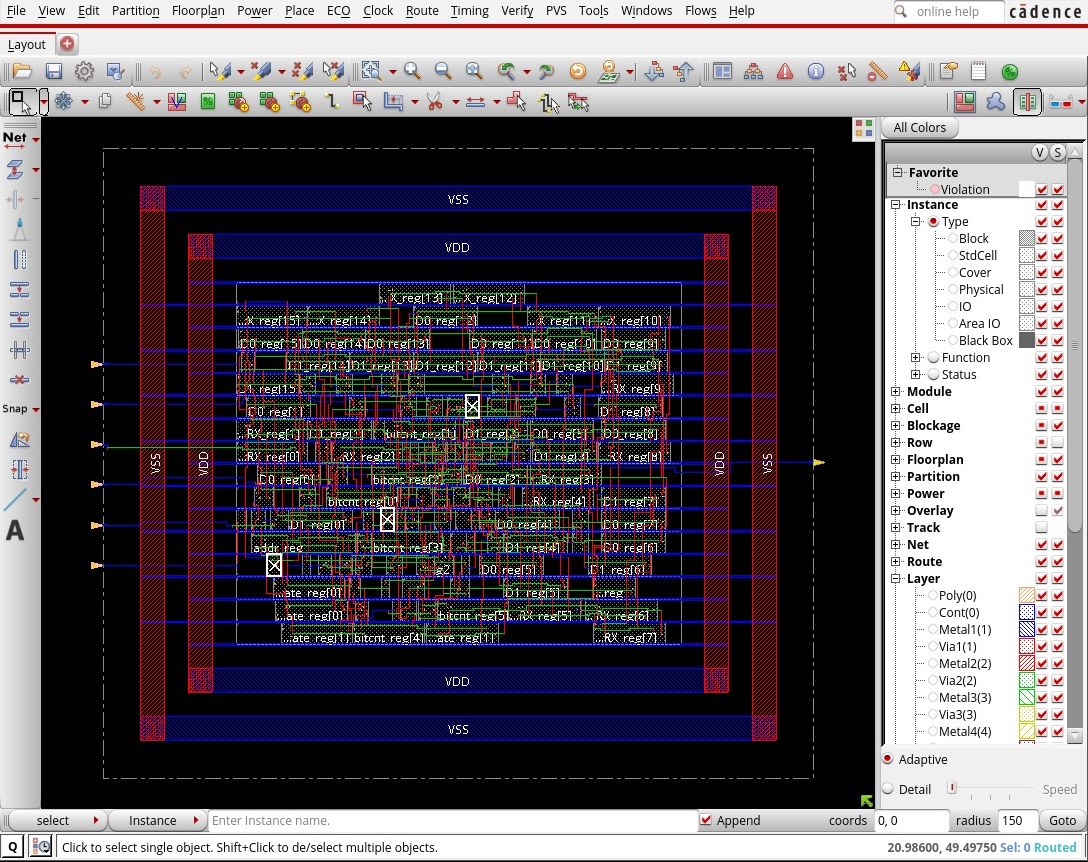

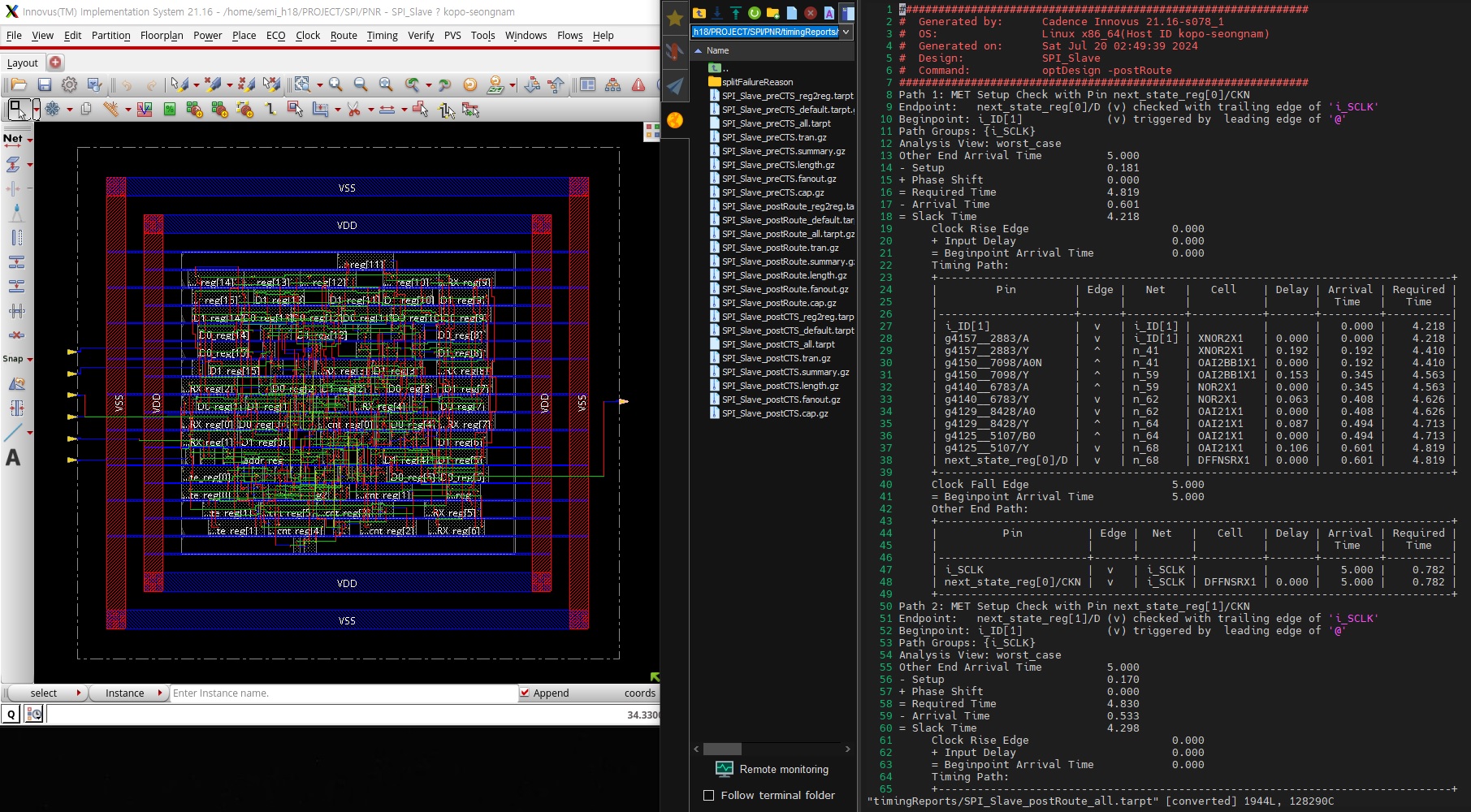

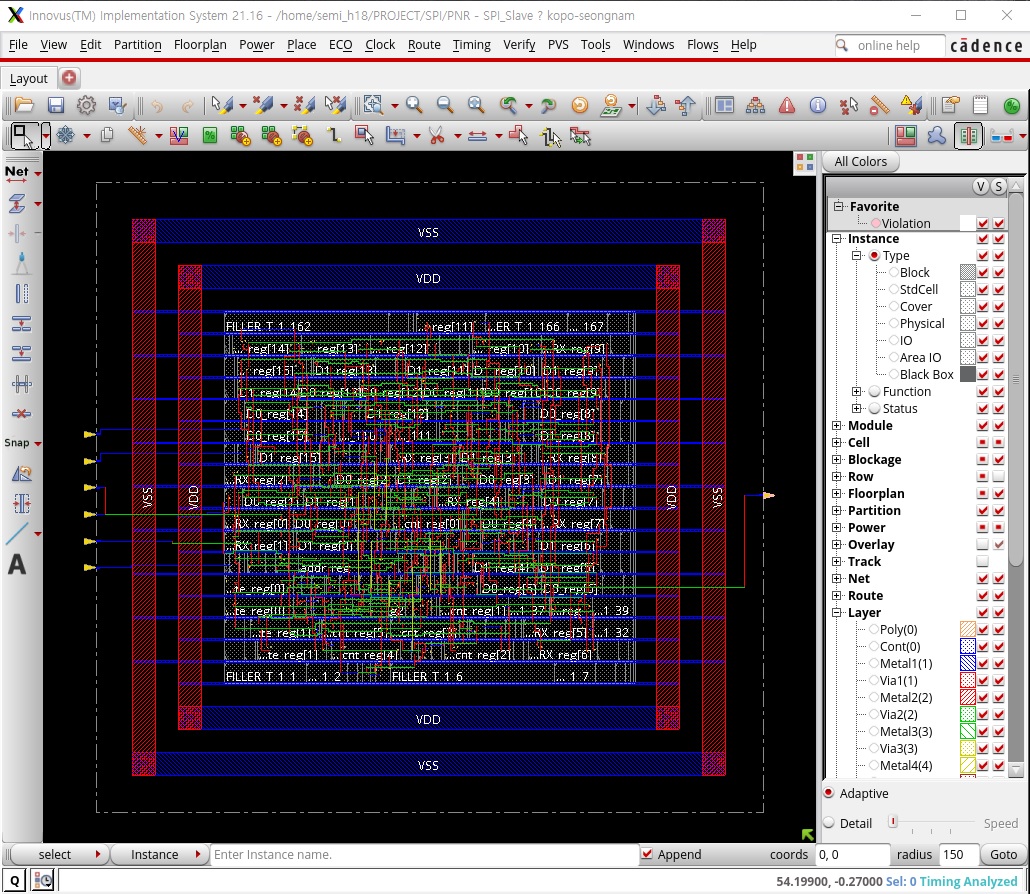

3. P&R

Tool은 Innovus를 사용하였으며, 자세한 과정은 생략하고 각 단계에서의 사진으로 대체하고,

마지막에 Script로 공유하도록 하겠습니다.

원래는 P&R 이전에 Timing 분석을 해야 하지만, Tool이 없는 관계로

각 단계에서 모두 Slack Time이 양수인지 확인하는 것으로 대체하겠습니다.

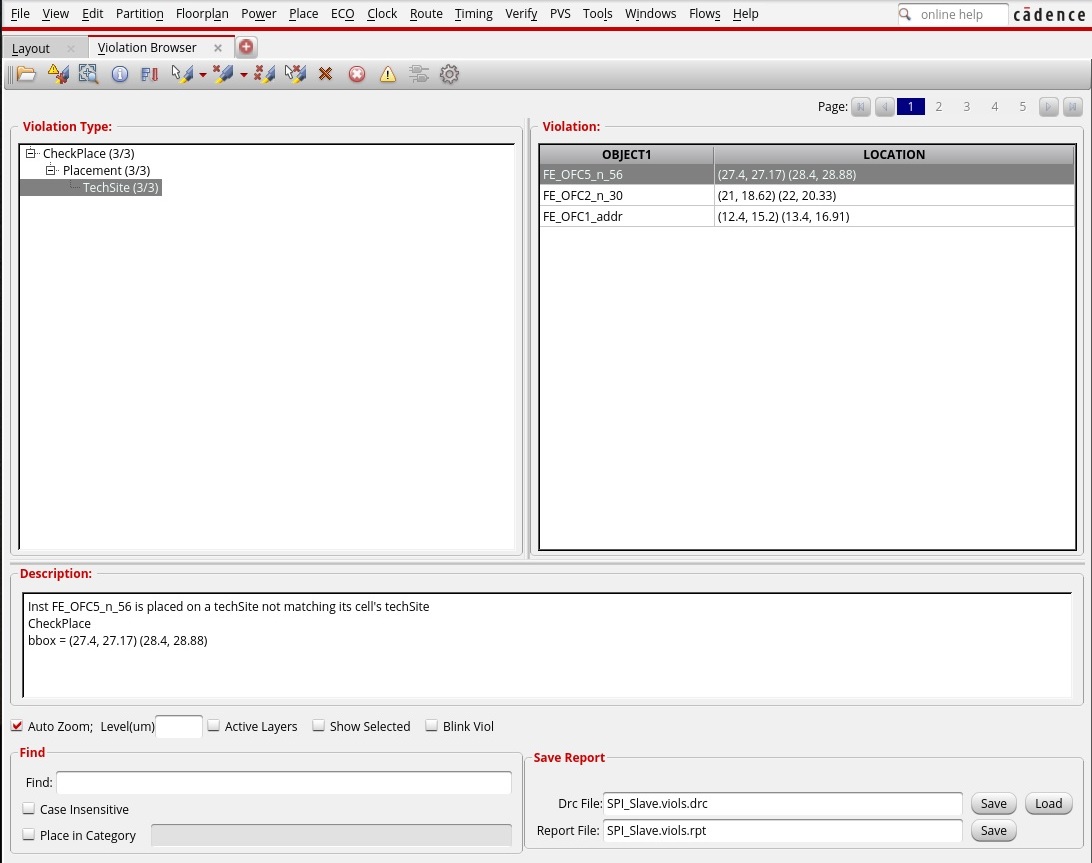

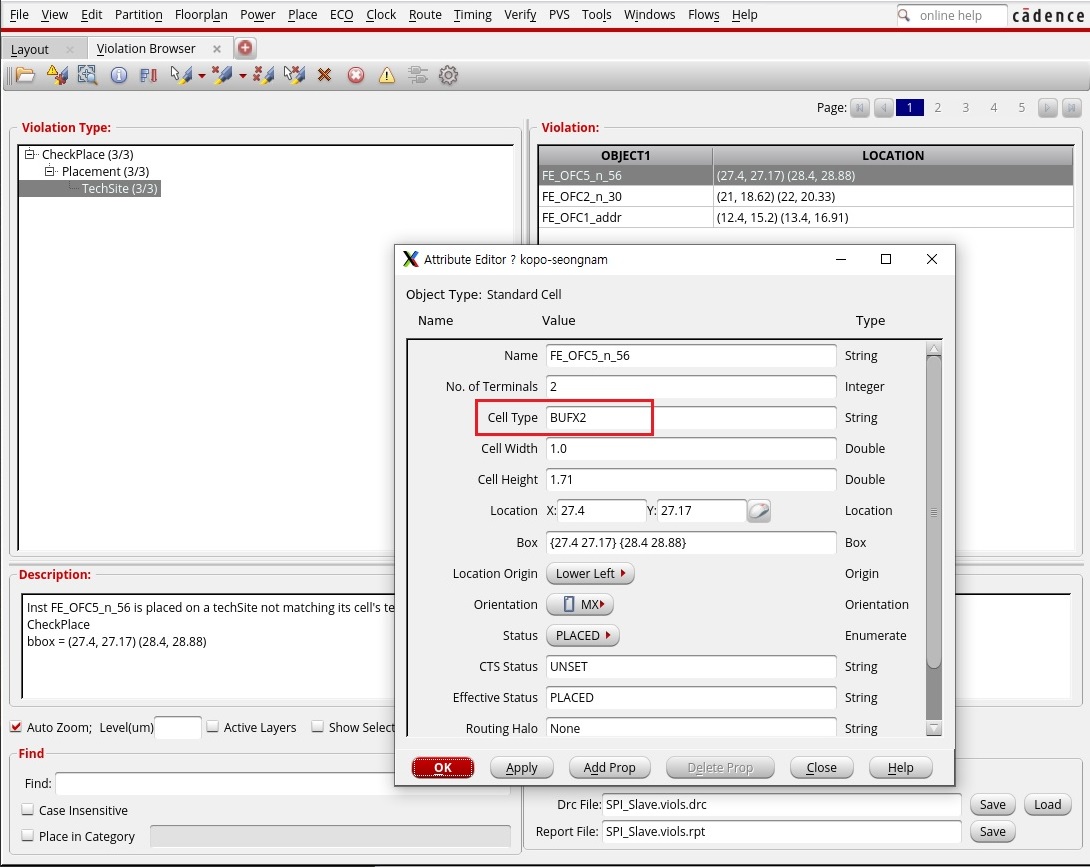

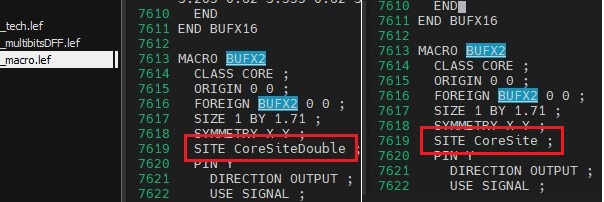

- Site Error

시작하자마자 문제가 생겼는데요,

Violation이 생겼습니다.

techSite 문제가 생긴 것 같은데요.

문제가 생긴 Object들이 모두 BUFX2 Cell에 있습니다.

BUFX2 Cell의 Site에 문제가 있는 것 같습니다.

교육용으로 사용하던 macro.lef 파일에 Site 이름이 잘못되어 있었는데요.

BUFX2 SITE를 CoreSiteDouble에서 CoreSite로 변경하였습니다.

- Pre-CTS

- Post-CTS

- Post-Route

- Result

이후 문제가 없이 잘 진행되었습니다.

결과적으로 Filler까지 추가한 다음 GDS 파일을 준비해놓고,

Post-Layout Simulation을 위한 netlist 파일과 sdf 파일을 준비합니다.

아래는 일련의 과정들을 cmd log로부터 추출하여 script로 만든 코드입니다.

- run_innovus.tcl

#Design Import

set init_gnd_net VSS

set init_lef_file {../../../LIB/lef/tech.lef ../../../LIB/lef/macro.lef}

set init_verilog ../../SYN/Output/SPI_Slave_netlist.v

set init_mmmc_file Default_01.view

set init_pwr_net VDD

init_design

#Floorplan

floorPlan -site CoreSite -r 0.921979067555 0.699987 10.0 10 10 10

#Power Planning

## Power-Connect Globalnets

clearGlobalNets

globalNetConnect VDD -type pgpin -pin VDD -instanceBasename * -hierarchicalInstance {}

globalNetConnect VSS -type pgpin -pin VSS -instanceBasename * -hierarchicalInstance {}

## Pin Assign

getPinAssignMode -pinEditInBatch -quiet

setPinAssignMode -pinEditInBatch true

editPin -fixOverlap 1 -unit MICRON -spreadDirection clockwise -side Left -layer 1 -spreadType center -spacing 3 -pin {i_CS {i_ID[0]} {i_ID[1]} i_MOSI i_rst_H i_SCLK}

setPinAssignMode -pinEditInBatch false

getPinAssignMode -pinEditInBatch -quiet

setPinAssignMode -pinEditInBatch true

editPin -fixOverlap 1 -unit MICRON -spreadDirection clockwise -side Right -layer 1 -spreadType center -spacing 3 -pin o_MISO

setPinAssignMode -pinEditInBatch false

## Add Ring

set sprCreateIeRingOffset 1.0

set sprCreateIeRingThreshold 1.0

set sprCreateIeRingJogDistance 1.0

set sprCreateIeRingLayers {}

set sprCreateIeRingOffset 1.0

set sprCreateIeRingThreshold 1.0

set sprCreateIeRingJogDistance 1.0

set sprCreateIeRingLayers {}

set sprCreateIeStripeWidth 10.0

set sprCreateIeStripeThreshold 1.0

set sprCreateIeStripeWidth 10.0

set sprCreateIeStripeThreshold 1.0

set sprCreateIeRingOffset 1.0

set sprCreateIeRingThreshold 1.0

set sprCreateIeRingJogDistance 1.0

set sprCreateIeRingLayers {}

set sprCreateIeStripeWidth 10.0

set sprCreateIeStripeThreshold 1.0

setAddRingMode -ring_target default -extend_over_row 0 -ignore_rows 0 -avoid_short 0 -skip_crossing_trunks none -stacked_via_top_layer Metal11 -stacked_via_bottom_layer Metal1 -via_using_exact_crossover_size 1 -orthogonal_only true -skip_via_on_pin { standardcell } -skip_via_on_wire_shape { noshape }

addRing -nets {VDD VSS} -type core_rings -follow core -layer {top Metal1 bottom Metal1 left Metal2 right Metal2} -width {top 1.8 bottom 1.8 left 1.8 right 1.8} -spacing {top 1.8 bottom 1.8 left 1.8 right 1.8} -offset {top 1.8 bottom 1.8 left 1.8 right 1.8} -center 0 -threshold 0 -jog_distance 0 -snap_wire_center_to_grid None

#Power Routing

setSrouteMode -viaConnectToShape { noshape }

sroute -connect { blockPin padPin padRing corePin floatingStripe } -layerChangeRange { Metal1(1) Metal11(11) } -blockPinTarget { nearestTarget } -padPinPortConnect { allPort oneGeom } -padPinTarget { nearestTarget } -corePinTarget { firstAfterRowEnd } -floatingStripeTarget { blockring padring ring stripe ringpin blockpin followpin } -allowJogging 1 -crossoverViaLayerRange { Metal1(1) Metal11(11) } -nets { VDD VSS } -allowLayerChange 1 -blockPin useLef -targetViaLayerRange { Metal1(1) Metal11(11) }

#Placement

setPlaceMode -fp false

place_design

## Violation Check

checkPlace SPI_Slave.checkPlace

setDrawView place

fit

#CTS & Routing

## Pre-CTS (ECO - Optimize Design)

setOptMode -fixCap true -fixTran true -fixFanoutLoad false

optDesign -preCTS

## Timing Report (Timing - Report timing, OutDir => timingReports Slack time must be (+)value)

redirect -quiet {set honorDomain [getAnalysisMode -honorClockDomains]} > /dev/null

timeDesign -preCTS -pathReports -drvReports -slackReports -numPaths 50 -prefix simple_spi_preCTS -outDir timingReports

## Route-Nano Route

setNanoRouteMode -quiet -routeTopRoutingLayer 11

setNanoRouteMode -quiet -routeBottomRoutingLayer 1

setNanoRouteMode -quiet -drouteEndIteration 1

setNanoRouteMode -quiet -routeWithTimingDriven false

setNanoRouteMode -quiet -routeWithSiDriven false

routeDesign -globalDetail

## Post-CTS

setOptMode -fixCap true -fixTran true -fixFanoutLoad false

optDesign -postCTS

## Post Routing(Tool - Set Mode - Specify Analysis Mode - On-chip Variation)

setAnalysisMode -cppr none -clockGatingCheck true -timeBorrowing true -useOutputPinCap true -sequentialConstProp false -timingSelfLoopsNoSkew false -enableMultipleDriveNet true -clkSrcPath true -warn true -usefulSkew true -analysisType onChipVariation -log true

setNanoRouteMode -quiet -routeWithTimingDriven false

setNanoRouteMode -quiet -routeWithSiDriven false

routeDesign -globalDetail

## Post-Route

setOptMode -fixCap true -fixTran true -fixFanoutLoad false

setDelayCalMode -engine default -siAware true

optDesign -postRoute

#Filler

getFillerMode -quiet

addFiller -cell FILL64 FILL32 FILL16 FILL8 FILL4 FILL2 FILL1 -prefix FILLER

#Verify

getMultiCpuUsage -localCpu

get_verify_drc_mode -disable_rules -quiet

get_verify_drc_mode -quiet -area

get_verify_drc_mode -quiet -layer_range

get_verify_drc_mode -check_ndr_spacing -quiet

get_verify_drc_mode -check_only -quiet

get_verify_drc_mode -check_same_via_cell -quiet

get_verify_drc_mode -exclude_pg_net -quiet

get_verify_drc_mode -ignore_trial_route -quiet

get_verify_drc_mode -max_wrong_way_halo -quiet

get_verify_drc_mode -use_min_spacing_on_block_obs -quiet

get_verify_drc_mode -limit -quiet

set_verify_drc_mode -disable_rules {} -check_ndr_spacing auto -check_only default -check_same_via_cell true -exclude_pg_net false -ignore_trial_route false -ignore_cell_blockage false -use_min_spacing_on_block_obs auto -report SPI_Slave.drc.rpt -limit 1000

verify_drc

set_verify_drc_mode -area {0 0 0 0}

#GDSII (save)

## save design

saveDesign SPI_Slave_complete

## save gds

streamOut SPI_Slave.gds -libName DesignLib -units 2000 -mode ALL

## save netlist

saveNetlist SPI_Slave_PNR.v

## save sdf

write_sdf -ideal_clock_network SPI_Slave_PNR.sdf

script로 만들어두면, 문제가 생겼을 때 손으로 다시 하는 것이 아니라,

다음 명령어로 빠르게 코드로 진행할 수 있습니다.

innovus -files run_innovus.tcl

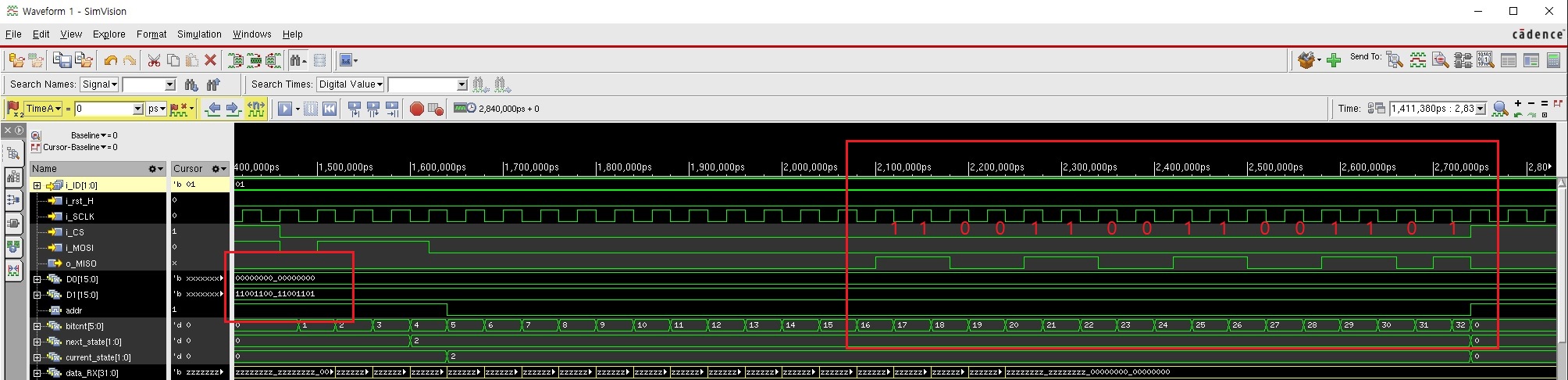

4. Post-Layout Simulation

P&R로부터 나온 SPI_Slave_PNR.v 파일과,

테스트벤치에 SPI_Slave_delay_PNR.sdf 파일을 연결시켜 시뮬레이션합니다.

Post_Sim 역시 기대하던 결과가 잘 나오는 것을 알 수 있습니다.

원래는 더 다양한 테스트 케이스 등 검증해야 할 것이 많지만

현재는 간단한 동작을 테스트 중이므로 이것으로 마무리합니다.

- 다음 글

(3) Arduino로 FPGA Motor 제어 : https://chonh0531.tistory.com/4

SPI 통신 - (3) Arduino로 FPGA Motor 제어

- 이전 글(1) RTL : https://chonh0531.tistory.com/2(2) Synthesis, P&R : https://chonh0531.tistory.com/3목차1. 과제 개요2. 소스코드3. 실습 결과 1. 과제 개요이전에 구현해 본 SPI_Slave를 테스트해 보기로 하였고,Master

chonh0531.tistory.com

'RTL, Synthesis, P&R' 카테고리의 다른 글

| UART 통신 - (2) Arm보드로 FPGA LCD 제어 (0) | 2024.09.03 |

|---|---|

| UART 통신 - (1) RTL (0) | 2024.09.03 |

| 32-bit SPI Interface - (3) Arduino로 FPGA Motor 제어 (0) | 2024.09.03 |

| 32-bit SPI Interface - (1) RTL (0) | 2024.09.03 |

| 4-digit Counter with FPGA (0) | 2024.08.30 |